A lightweight educational implementation of the

AITL layered control architecture,

designed to clearly distinguish:

- ⚙️ runtime control responsibility

- 🧠 design-time intelligence

Inner Loop : PID Controller

Middle Loop: FSM (Finite State Machine, Safety & Mode Supervision)

Adaptive Assist Layer: NN / RL (bounded, runtime optional)

LLM: Offline / Non-Real-Time Design Assistant (A-type)

| Language | GitHub Pages 🌐 | GitHub 💻 |

|---|---|---|

| 🇺🇸 English |  |

|

📐 Official Architecture Definition & Reliability Boundary of AITL Controller (A-Type)

This page defines the design rationale, operating assumptions,

and verified reliability limits of the AITL architecture.

⚠️ Important Architectural ClarificationIn practical runtime systems, the valid control configurations are:

- ✅ PID × FSM

- ✅ PID × FSM × NN / RL (bounded)

❌ LLM is never placed inside the real-time control loop

LLM is used exclusively outside real-time operation for:

- analysis

- design review

- architecture exploration

- documentation and explanation

This project demonstrates a clear and modular control-design methodology,

not the pursuit of:

- maximum performance

- autonomous intelligence

- black-box optimization

Instead, the emphasis is on:

- 🧩 architectural clarity

- 🛡 safety and determinism

- 📐 explicit responsibility separation

- 🧠 human-verifiable control logic

- PID handles continuous physical dynamics

- FSM governs discrete safety and mode transitions

- NN / RL may assist within bounded, supervised domains

- LLM supports design-time reasoning only

Intelligence is layered —

but responsibility is never ambiguous.

This controller is intended as a reference architecture,

suitable for:

- education

- architectural discussion

- early-stage system design

- safety-oriented control thinking

It is not intended as a drop-in production controller,

nor as a demonstration of autonomous AI control.

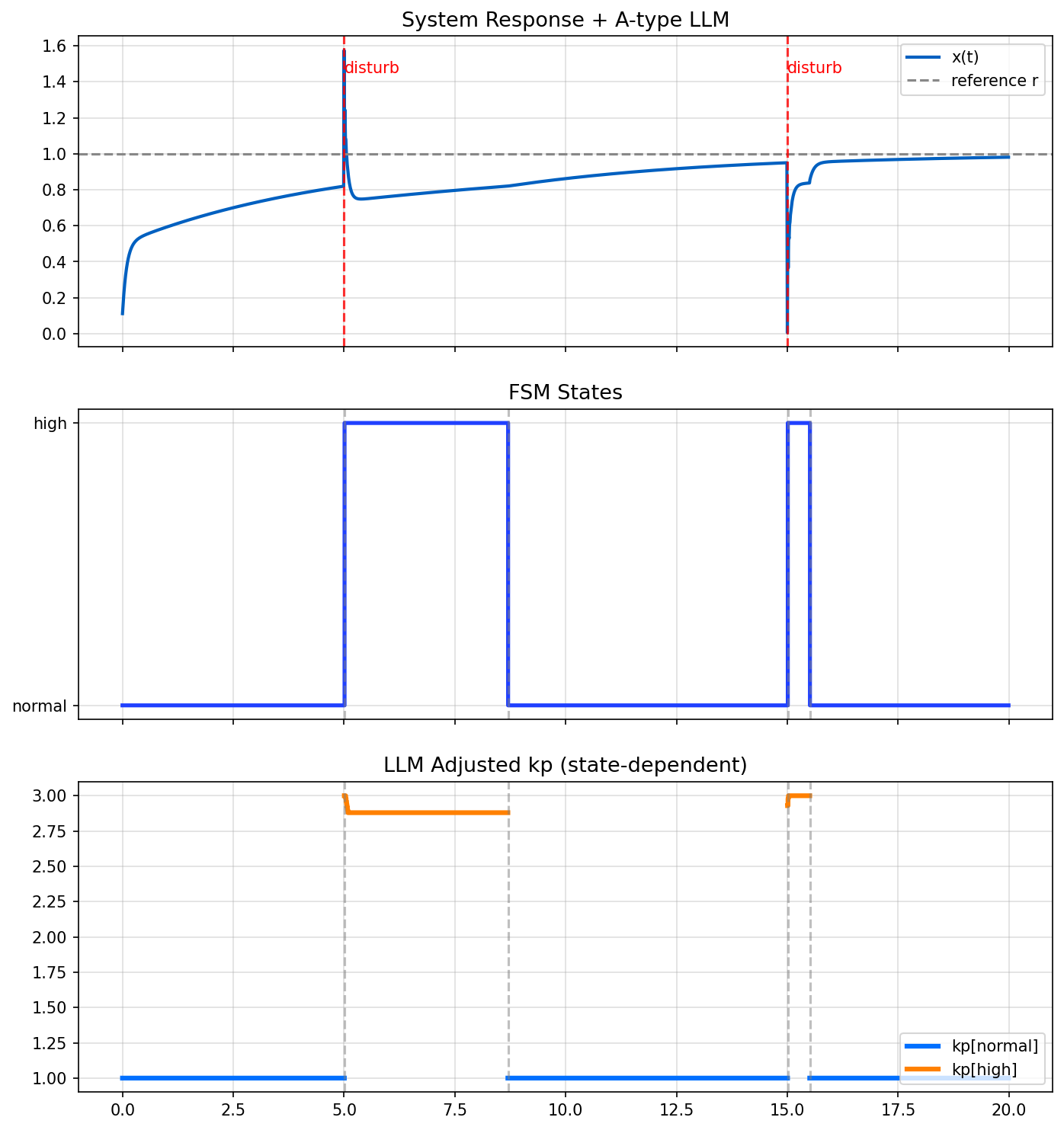

This figure is generated by:

demos/05_aitl_full_demo.py

Note

This demo visualizes the conceptual integration of the AITL architecture

under ideal conditions and does not imply that all components

operate simultaneously in real time.

AITL-CONTROLLER-A-TYPE/

│

├── src/

│ ├── controllers/

│ │ ├── pid.py

│ │ ├── fsm.py

│ │ ├── hybrid.py

│ │

│ ├── models/

│ │ └── llm.py

│ │

│ └── core/

│ └── base.py

│

├── demos/

│ ├── 01_pid_step_response.py

│ ├── 02_fsm_mode_switch.py

│ ├── 03_hybrid_pid_fsm_demo.py

│ ├── 04_hybrid_fsm_llm_demo.py

│ ├── 05_aitl_full_demo.py

│ │

│ ├── 12_vi_current_control_sales_demo.py

│ │ └─ V–I current control comparison under aging & disturbance

│ ├── 13_aging_sweep_delta_t.py

│ │ └─ reliability metrics sweep (Δt, max|e| vs aging)

│ └── 15_fsm_explainability_demo.py

│ └─ FSM explainability & audit-ready transition rationale

│

├── data/

│ ├── aitl_full_demo_ideal.png

│ ├── aitl_full_demo_ideal.pdf

│ │

│ ├── 12_vi_current_control_sales_demo.png

│ │ └─ waveform comparison (Fixed PID / PID×FSM / AITL)

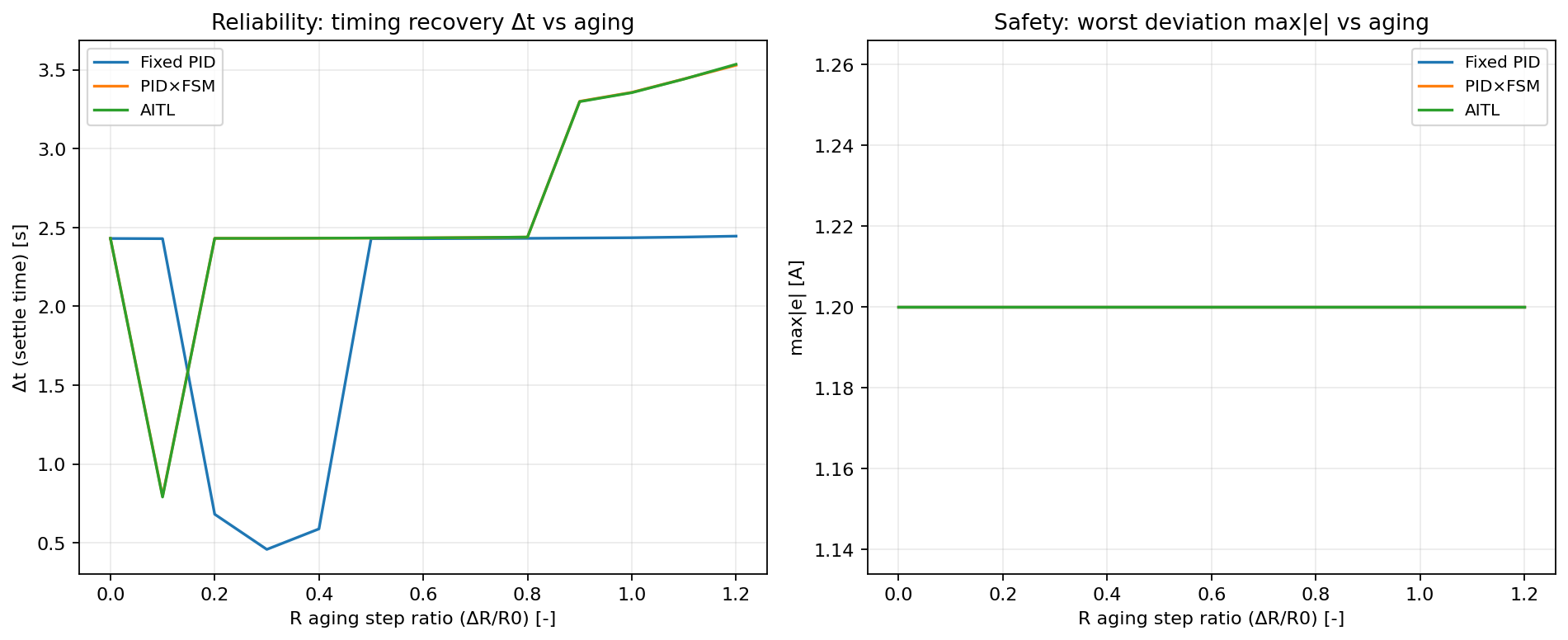

│ ├── 13_aging_sweep_delta_t.png

│ │ └─ quantitative reliability & safety metrics

│ └── 15_fsm_explainability_demo.png

│ └─ explainable FSM mode switching visualization

│

├── tests/

│

├── paper.pdf

└── README.md

- ⏱️ variable sampling period

dt - 🔄 integral & derivative reset

- 🎚️ normal / high-response gain profiles

Role:

🛡️ Provides deterministic stability and baseline performance in real time.

Switching logic:

normal → high (if |error| > threshold_high)

high → normal (if |error| < threshold_low)

🧩 Provides explainable and auditable control-mode transitions.

Role:

- 🧯 supervises safety and mode selection

- 🚦 gates whether adaptive assistance is permitted

- ↩️ provides explicit fallback behavior

- 📐 applies a bounded assist term under FSM supervision

- ⚡ improves recovery timing only within a verified operating region

- 🎓 educational and reproducible

(not a claim of universal optimality)

⚠️ Note (Runtime Validity):

The recommended runtime configurations are

PID × FSM and PID × FSM × NN/RL (bounded).

- 📴 used exclusively outside the real-time control loop

- 📊 supports log analysis, design review, and documentation

- 🛠️ may propose parameter updates, but does not execute control actions in real time

🚫 Strict prohibitions:

- ❌ no real-time I/O

- ❌ no direct gain injection during runtime

- ❌ no FSM state or transition control

| Script | Description |

|---|---|

01_pid_step_response.py |

Basic PID response (baseline behavior) |

02_fsm_mode_switch.py |

FSM threshold-based mode switching |

03_hybrid_pid_fsm_demo.py |

PID × FSM hybrid control (runtime reference) |

04_hybrid_fsm_llm_demo.py |

Offline design-support demo (LLM is not in the real-time loop) |

05_aitl_full_demo.py |

Conceptual AITL integration demo (ideal condition visualization) |

12_vi_current_control_sales_demo.py |

V–I current control comparison under aging & disturbance (Fixed PID / PID × FSM / AITL) |

13_aging_sweep_delta_t.py |

Reliability metrics sweep vs aging (Δt, max e) |

15_fsm_explainability_demo.py |

FSM explainability demo (why and when modes switched) |

Note:

Demos 12, 13, and 15 provide quantitative and explainable evidence

supporting reliability-related design conclusions.

cd demos

python 05_aitl_full_demo.pyOutput:

../data/aitl_full_demo_ideal.png

- 🧱 emphasizes architecture over tuning

- 🔍 interpretable and FSM-supervised adaptive behavior

- 👀 visual understanding of mode switching and intervention

- 📚 suitable for teaching materials and research prototypes with auditability

- B-Type AITL (reliability permission layer)

- 🧠 advanced FSM with multi-modes / hysteresis

- 🔀 nonlinear plants

- 🎯 RL-based bounded adaptive tuning (ε-term, FSM-supervised)

- 🧩 integration with AITL-H system

Note (Scope Clarification):

LLM is not planned as a self-optimizing runtime controller.

Any use of LLM is restricted to offline analysis, design review, and documentation.

Purpose (Normative):

This investigation provides design evidence to identify

the operational reliability boundary of A-Type.

It does not modify runtime control authority.

Beyond ideal conditions, the AITL controller was evaluated under

severe long-term plant degradation, modeled as

friction aging equivalent to 1000 days.

The objective of this investigation is not to claim superiority,

but to identify the operational boundary of adaptive control.

The primary focus is temporal reliability:

- ⏱️ recovery timing consistency (Δt)

- 🔎 degradation detectability

- 🚫 explicit criteria for when adaptation must be restricted

This result demonstrates that:

- 📉 all controllers degrade as plant aging progresses

- 📈 AITL improves recovery timing only within a limited aging range

- ⛔ beyond that range, continued adaptation does not preserve temporal reliability

- 📐 the degradation trend is explicitly measurable via Δt

Crucially, this means:

AITL is effective only within a clearly identifiable operating region.

Outside that region, adaptation must be restricted or stopped by design.

This analysis does not argue that AITL is universally better.

Instead, it establishes that:

- 🧭 adaptive control has a finite, observable reliability boundary

- 🚨 that boundary can be detected before instability or failure

- 🧮 Δt serves as a design-time and run-time decision metric

In other words, the result answers:

“Until when is AITL safe to use?”

—not merely “Does it work?”

This finding directly motivates a reliability-first extension:

- A-Type: demonstrates adaptive capability

- B-Type: decides whether adaptation should be allowed

The reliability investigation provides the evidence layer

that makes B-Type a necessary architectural evolution,

not a conceptual add-on.

Detailed waveforms, quantitative metrics, and explainable supervisory logic

are documented separately.

👉 Full reliability analysis (reproducible evidence):

AITL is not always beneficial — and that fact is measurable.

This investigation identifies the operating region

where adaptive control should be applied — and where it should not.

The A-Type results demonstrate that adaptive control has a finite reliability boundary.

Beyond a certain aging or degradation range, continued adaptation may degrade

temporal reliability (Δt) rather than improve performance.

B-Type is a design extension that transforms this empirical boundary into an explicit operational rule by introducing a dedicated reliability permission layer.

B-Type does not aim to maximize performance.

Instead, it determines whether adaptation is permitted based on

monitored reliability conditions.

Typical monitored quantities include:

- ⏱️ Δt: recovery time / temporal reliability

- 📏 max‖e‖: safety envelope (worst-case deviation)

- 🎚️ ‖ΔKp‖ or dKp/dt: adaptation aggressiveness (stability risk)

A-Type proves adaptation capability.

B-Type enforces adaptation responsibility.

Adaptive tuning is enabled only when reliability metrics satisfy design-time acceptance criteria. If these conditions are violated, the system restricts adaptation and falls back to a conservative operating mode (e.g., fixed-gain PID control).

👉 B-Type Design Documentation (architecture & guard logic)

→ docs/b_type/

While A-Type demonstrates adaptive capability

and B-Type enforces reliability and responsibility,

True Robust Control addresses a deeper question:

How should robustness itself be operated

before theoretical guarantees collapse?

This theme extends the AITL framework by treating robustness

not as a fixed design result, but as an operational capability.

True Robust Control introduces the following design concepts:

- 🔄 Uncertainty Δ as an observable state, not a static worst-case bound

- 📡 Frequency-aware interpretation of degradation

- low-frequency: performance degradation

- high-frequency: stability margin loss

- input-side: actuator stress and saturation

- 🛑 Proactive intervention before robustness guarantees collapse

- 🧮 Selective redesign of robustness weight functions

-

$$W_s$$ : performance demand -

$$W_t$$ : robustness margin -

$$W_u$$ : actuator protection

-

- 🧱 Strict role separation

- FSM decides when to intervene

- LLM decides which design lever to move (offline only)

- Controllers execute safely without reasoning

| Layer | Primary Role |

|---|---|

| A-Type | Demonstrates adaptive capability |

| B-Type | Restricts adaptation for reliability |

| True Robust Control | Operates robustness as a dynamic design process |

A-Type asks: Can the system adapt?

B-Type asks: Should the system adapt?

True Robust Control asks: How should robustness be operated?

These layers are complementary, not competing.

📘 True Robust Control — Design Documentation

→ docs/true_robust_control/

This section is recommended when:

- H∞ control feels too static or overly conservative

- plant degradation evolves over time

- robustness decisions must be explainable and auditable

- design intervention must occur before instability

| 📌 Item | License | Description |

|---|---|---|

| Source Code | MIT License | Free to use, modify, and redistribute |

| Text Materials | CC BY 4.0 or CC BY-SA 4.0 | Attribution required; share-alike applies for BY-SA |

| Figures & Diagrams | CC BY-NC 4.0 | Non-commercial use only |

| External References | Follow the original license | Cite the original source properly |

Suggestions, improvements, and discussions are welcome via GitHub Discussions.